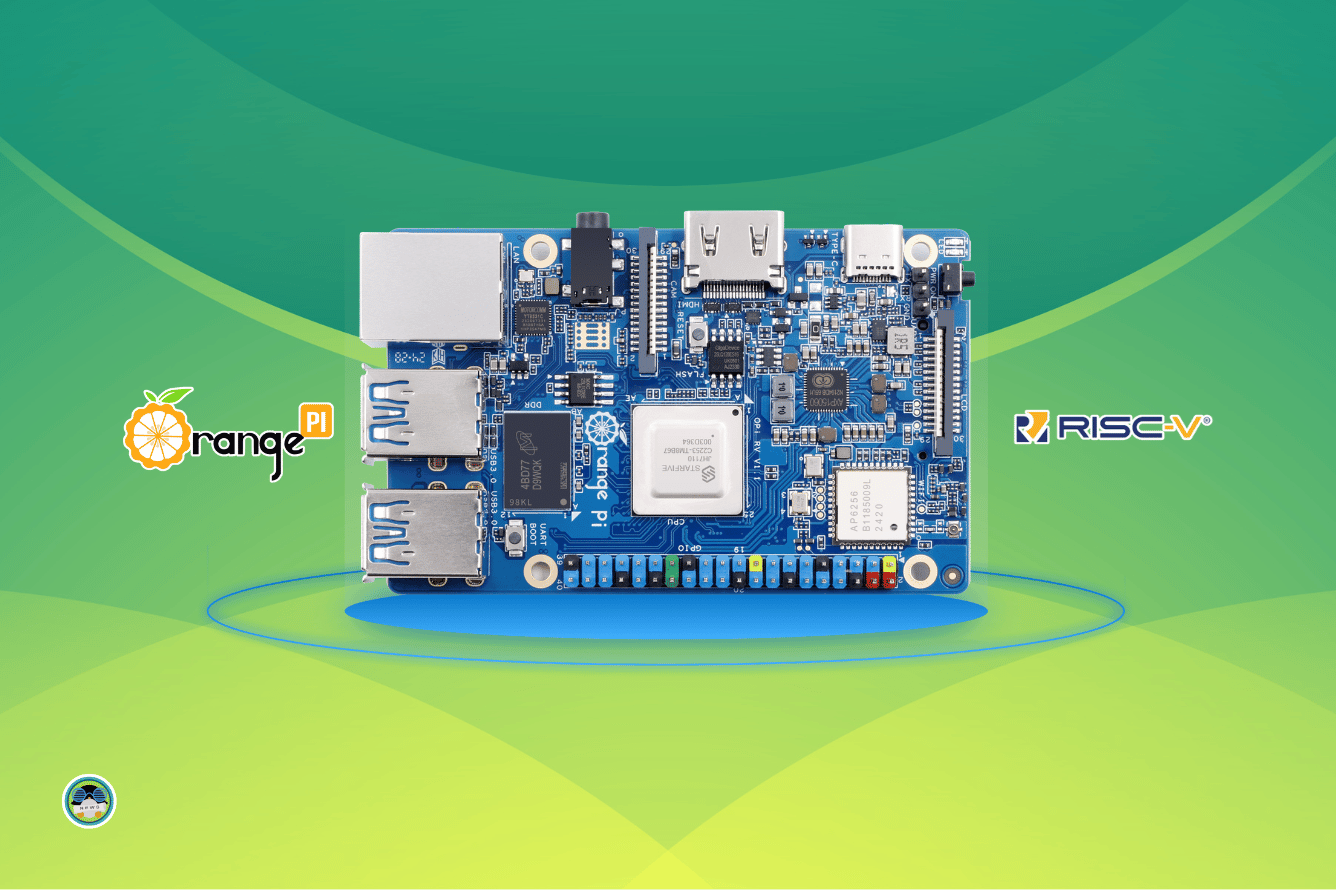

#OrangePi Now has an #OpenSource #RISC-V SBC [With M.2 Slot]

source: https://news.itsfoss.com/orange-pi-rv/

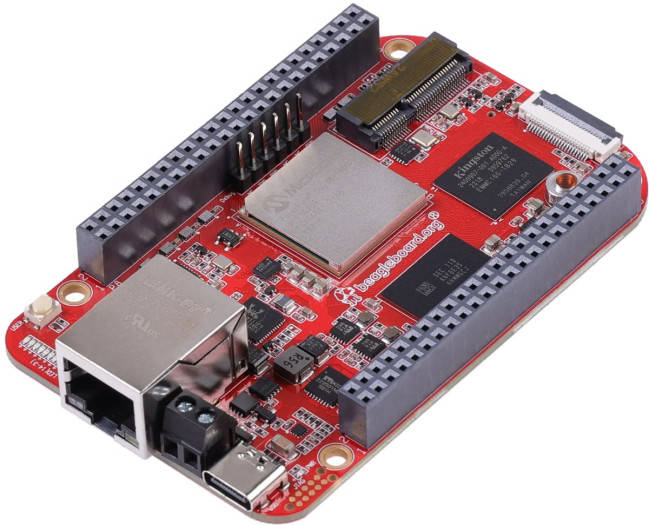

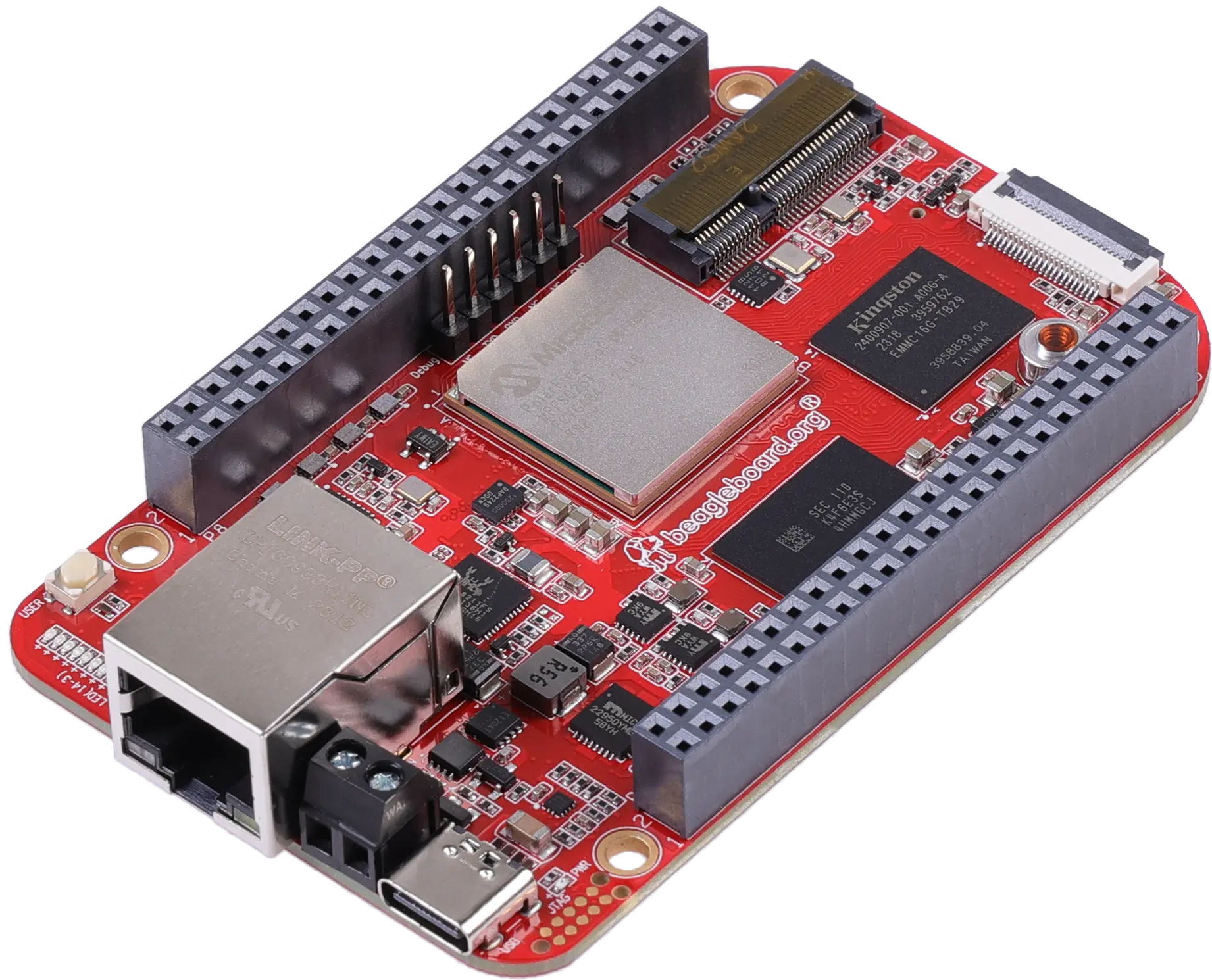

TL;DR: The #CPU is too weak for a #desktop system. Without #HDMI, there are much cheaper IoT RISC-V systems.

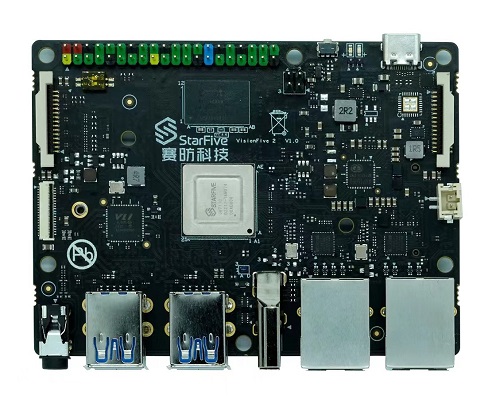

The RISC-V chip it uses is the same one as found on the #Milk-V Mars, with Orange Pi pointing out that it can run Linux distributions, pointing to #Debian #Linux on its download page.

With Milk-V Mars, starting #Firefox takes 20 seconds under Debian. Nobody really wants to work with this #performance. You could certainly shorten the time with a very lightweight customized Linux, but it is questionable whether these adjustments will be made.

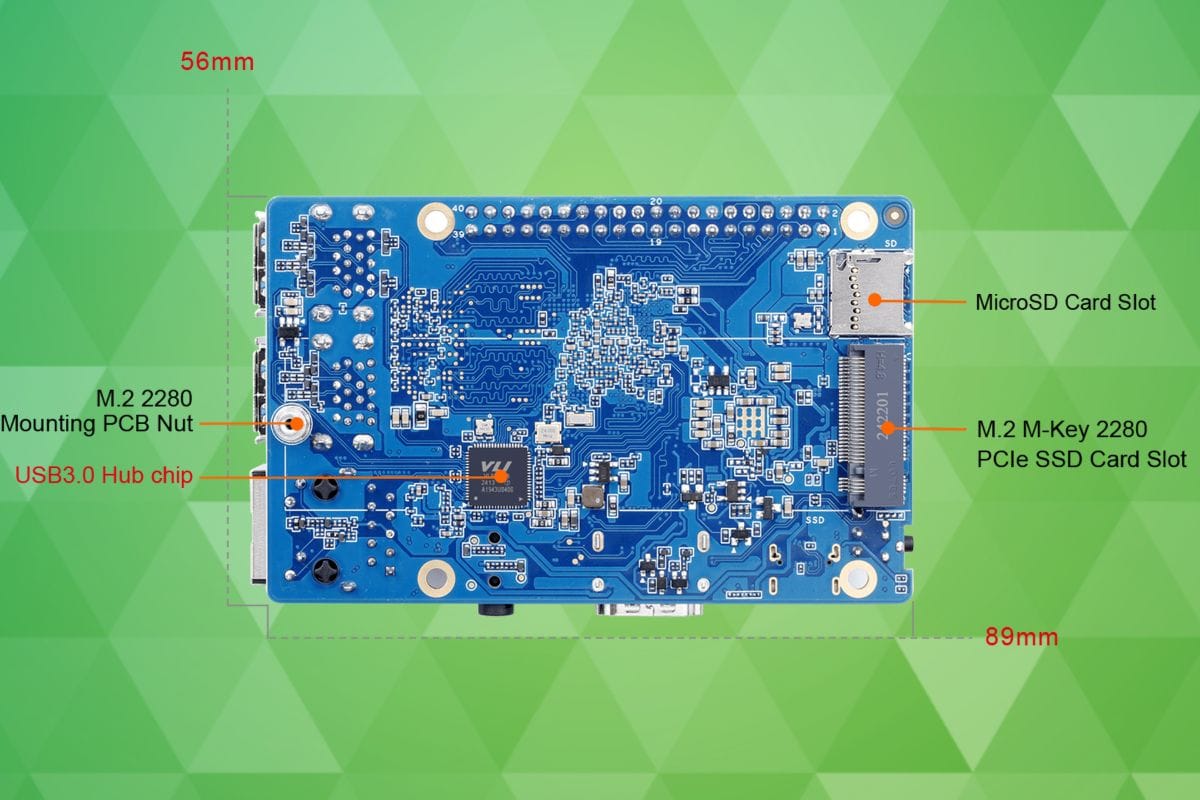

What's better is that #PCIe is on the underside, unlike the Mars, and the #Wifi is onboard.

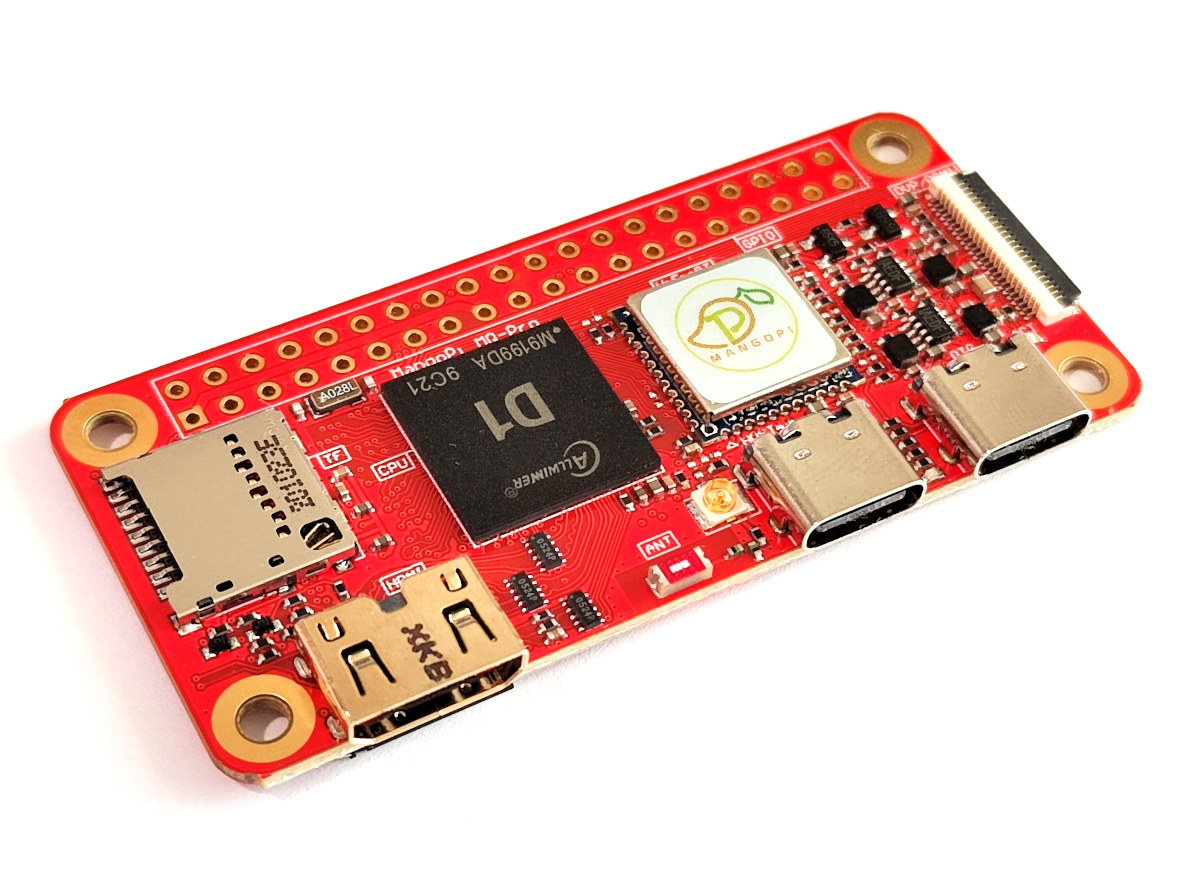

If you are looking for a pure IoT solution without HDMI, the Milk-V Duo S is a much cheaper hardware that runs under Linux.

/cloudfront-us-east-2.images.arcpublishing.com/reuters/V2B22MP4LFN4NPU3BOVIYIPJ4Y.jpg)